1

# Opportunities and Design Considerations of GaN HEMTs in ZVS Applications

## Juncheng (Lucas) Lu, Ruoyu Hou, and Di Chen GaN Systems Inc.

- 2. Loss Model of GaN HEMTs in ZVS Applications

- 3. Package Considerations

- 4. Conclusions

Systems

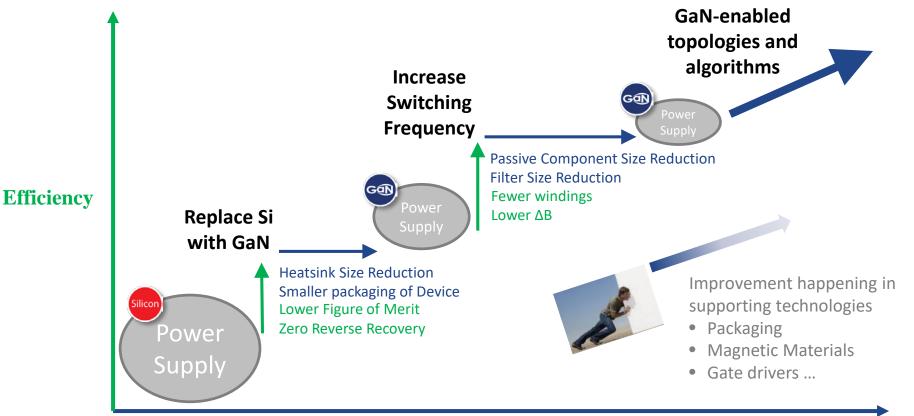

### **GaN HEMTs today**

#### **Consumer**

### #1 in GaN

- Highest current; broadest voltages

- Best electrical performance

- Best die & best package

- Most widely used by customers

### Shipping since 2014

- Offices in 7 countries

- Worldwide disti & direct sales

### **Customer successes**

- Solar Inverter and ESS

- Motor Drives

- Wireless Power and Charging

- AC Adapters

- Datacenter Server and Rack Power

- Automotive Onboard Charger

#### **Power Density**

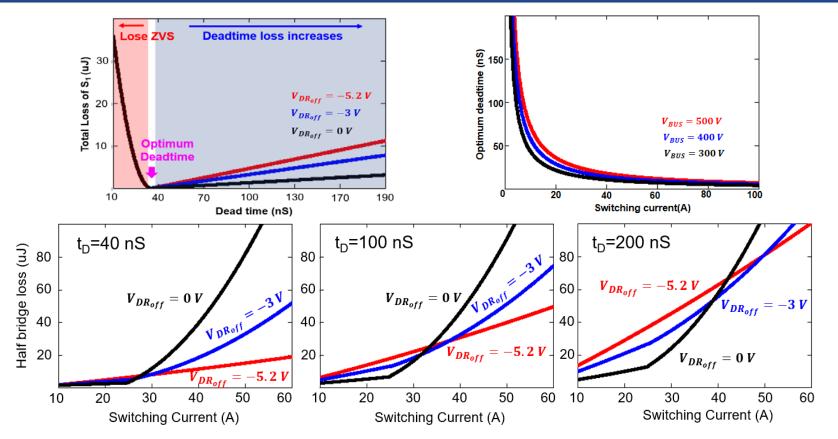

## **APEC** Loss Model of GaN HEMTs in ZVS Applications **Gan** Systems

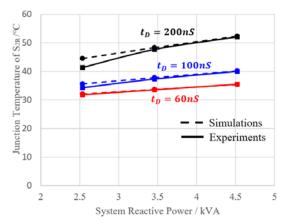

Half-bridge overall loss vs. switching current under different negative turn-off gate voltage  $V_{DRoff}$  (a) with deadtime  $t_D$ =40 nS, (b) with deadtime  $t_D$ =100 nS, (c) with deadtime  $t_D$ =200 nS.

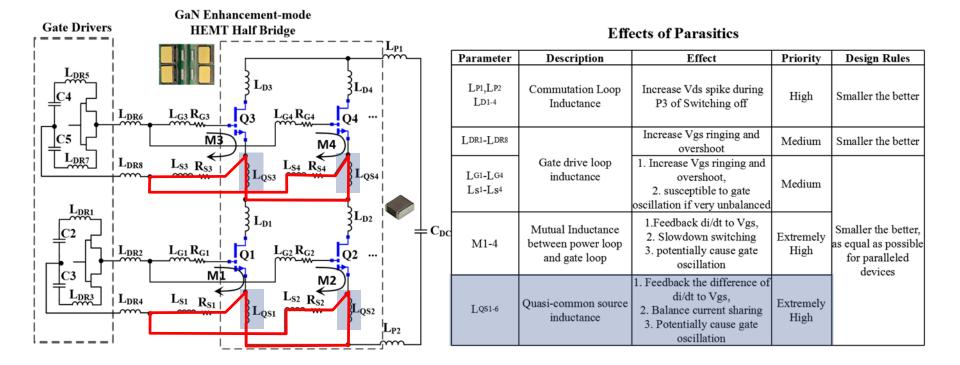

### **Key Parasitics for Paralleling** [1]

### **Parasitics Optimization** is the key to the ultra-high performance of GaN HEMT.

[1] J. L. Lu and D. Chen, "Paralleling GaN E-HEMTs in 10kW–100kW systems," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, 2017, pp. 3049-3056. doi: 10.1109/APEC.2017.7931131

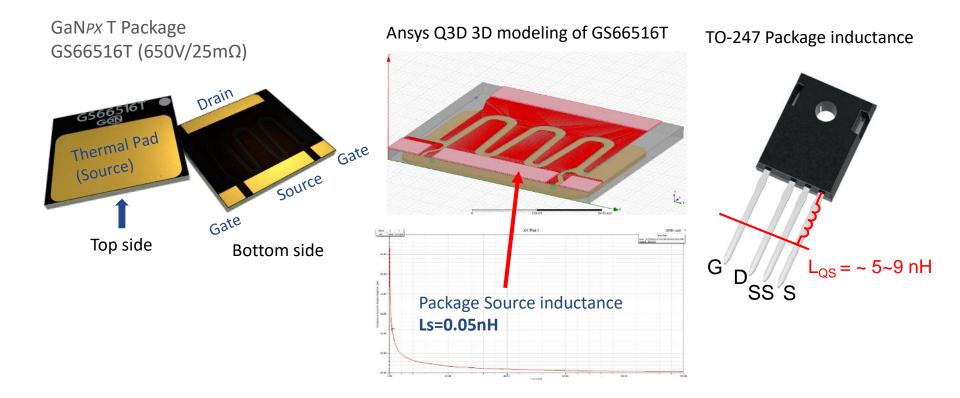

# **APEC** Packaging Parasitics of Power Semi-conductors **Gan** Systems

### GaNPX has ultra-low Ls compared to traditional package.

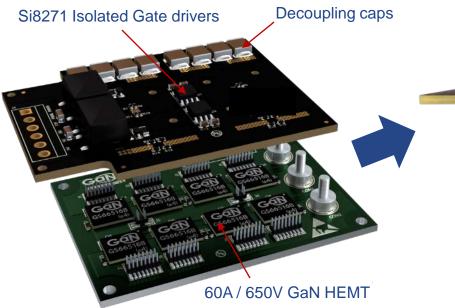

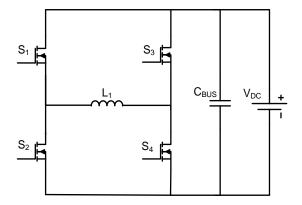

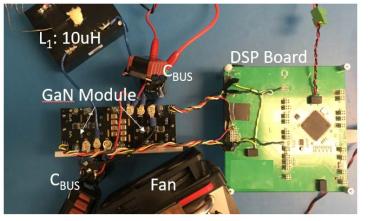

# **APEC** Reference Design of 240A/650V GaN Module

- Gate driver board design concept

- Assemble on top of IMS(metal core) boards

Gate driver board Metal Core PCB

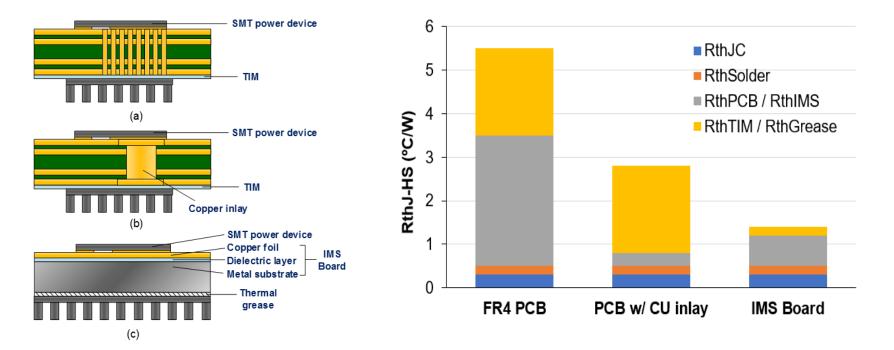

- More compact layout and lower stray inductance than traditional power module, optimized for high speed GaN

- Thermal resistance R<sub>thJC</sub> ~= 1°C/W

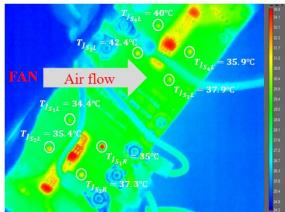

The thermal performance is enhanced compared with the PCB solution.

Systems

The thermal performance is enhanced compared with the PCB solution.

Systems

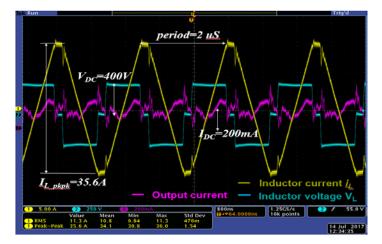

### **Experimental Results**

# Thank you! & Any questions?